# 3-Axis, $\pm 0.5 \ g/\pm 1 \ g/\pm 2 \ g/\pm 4 \ g$ Digital Accelerometer

Data Sheet ADXL313

#### **FEATURES**

Ultralow power (scales automatically with data rate) As low as 30  $\mu$ A in measurement mode (V<sub>S</sub> = 3.3 V) As low as 0.1  $\mu$ A in standby mode (V<sub>S</sub> = 3.3 V)

Low noise performance

150 μg/√Hz typical for X- and Y-axes 250 μg/√Hz typical for the Z-axis

Embedded, patent pending FIFO technology minimizes host processor load

**User-selectable resolution**

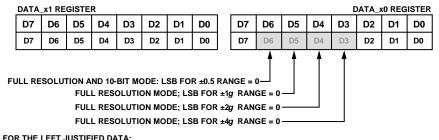

Fixed 10-bit resolution for any g range

Fixed 1024 LSB/g sensitivity for any g range

Resolution scales from 10-bit at  $\pm 0.5 g$  to 13-bit at  $\pm 4 g$

Built-in motion detection functions for activity/inactivity monitoring

Supply and I/O voltage range: 2.0 V to 3.6 V

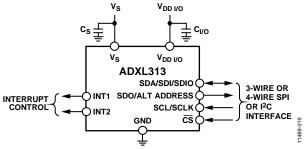

SPI (3-wire and 4-wire) and I<sup>2</sup>C digital interfaces

Flexible interrupt modes mappable to two interrupt pins

Measurement range selectable via serial command

Bandwidth selectable via serial command

Wide temperature range (-40°C to +105°C)

10,000 g shock survival

Pb free/RoHS compliant

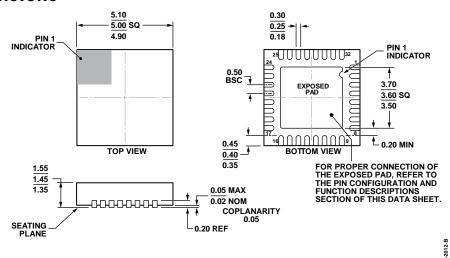

Small and thin: 5 mm  $\times$  5 mm  $\times$  1.45 mm LFCSP package

**Qualified for automotive applications**

#### **APPLICATIONS**

Car alarms

Hill start aid (HSA) systems

Electronic parking brakes

Data recorders (black boxes)

#### **GENERAL DESCRIPTION**

The ADXL313 is a small, thin, low power, 3-axis accelerometer with high resolution (13-bit) measurement up to  $\pm 4$  g. Digital output data is formatted as 16-bit twos complement and is accessible through either a serial port interface (SPI) (3-wire or 4-wire) or  $I^2C$  digital interface.

The ADXL313 is well suited for car alarm or black box applications. It measures the static acceleration of gravity in tilt-sensing applications, as well as dynamic acceleration resulting from motion or shock. Its high resolution (1024 LSB/g) and low noise (150  $\mu$ g/ $\sqrt{Hz}$ ) enable resolution of inclination changes of as little as 0.1°. A built-in FIFO facilitates using oversampling techniques to improve resolution to as little as 0.025° of inclination.

Several built-in sensing functions are provided. Activity and inactivity sensing detects the presence or absence of motion and whether the acceleration on any axis exceeds a user-set level. These functions can be mapped to interrupt output pins. An integrated 32-level FIFO can be used to store data to minimize host processor intervention, resulting in reduced system power consumption.

Low power modes enable intelligent motion-based power management with threshold sensing and active acceleration measurement at extremely low power dissipation.

The ADXL313 is supplied in a small, thin 5 mm  $\times$  5 mm  $\times$  1.45 mm, 32-lead LFCSP package and is pin compatible with the ADXL312 accelerometer device.

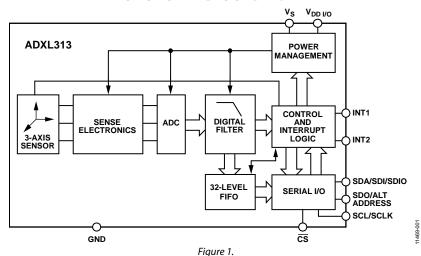

#### **FUNCTIONAL BLOCK DIAGRAM**

eedback

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

## **TABLE OF CONTENTS**

| reatures                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Functional Block Diagram                    | 1  |

| Revision History                            | 2  |

| Specifications                              | 3  |

| Absolute Maximum Ratings                    | 4  |

| Thermal Resistance                          | 4  |

| ESD Caution                                 | 4  |

| Pin Configuration and Function Descriptions | 5  |

| Typical Performance Characteristics         | 6  |

| Theory of Operation                         | 8  |

| Power Sequencing                            | 8  |

| Power Savings                               | 8  |

| Serial Communications                       | 10 |

| SPI                                         | 10 |

| I <sup>2</sup> C                            | 13 |

| Interrupts                                  | 15 |

| FIFO                                    | 15 |

|-----------------------------------------|----|

| Self Test                               | 16 |

| Register Map                            | 17 |

| Register Definitions                    | 18 |

| Applications Information                | 22 |

| Power Supply Decoupling                 | 22 |

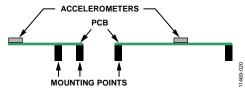

| Mechanical Considerations for Mounting  | 22 |

| Threshold                               | 22 |

| Link Mode                               | 22 |

| Sleep Mode vs. Low Power Mode           | 22 |

| Using Self Test                         | 23 |

| 3200 Hz and 1600 Hz ODR Data Formatting | 24 |

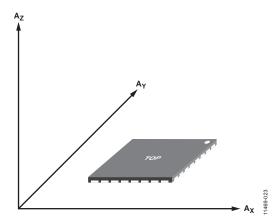

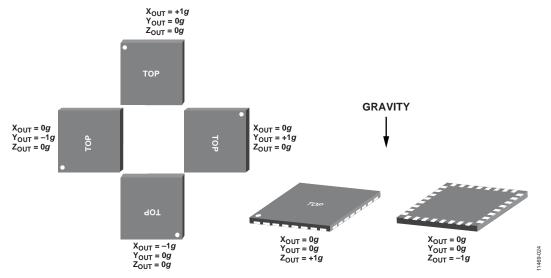

| Axes of Acceleration Sensitivity        | 25 |

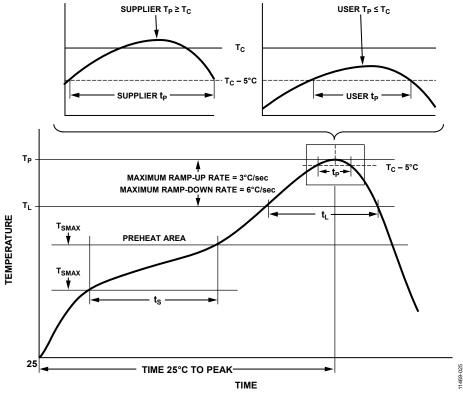

| Solder Profile                          | 26 |

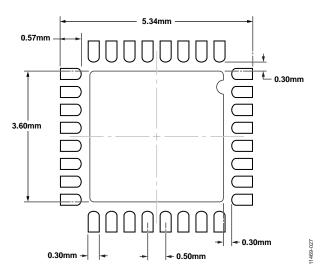

| Outline Dimensions                      | 27 |

| Ordering Guide                          | 28 |

| Automotive Products                     | 28 |

### **REVISION HISTORY**

4/13—Revision 0: Initial Version

## **SPECIFICATIONS**

$T_A = -40$ °C to +105°C,  $V_S = V_{DD I/O} = 3.3$  V, acceleration = 0 g, unless otherwise noted.

Table 1.

| Parameter <sup>1</sup>                                                | Test Conditions/Comments                                                             | Min   | Тур              | Max         | Unit            |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|------------------|-------------|-----------------|

| SENSOR INPUT                                                          | Each axis                                                                            |       |                  |             |                 |

| Measurement Range                                                     | User selectable                                                                      |       | ±0.5, ±1, ±2, ±4 |             | g               |

| Nonlinearity                                                          | Percentage of full scale                                                             |       | ±0.5             |             | %               |

| Micro-Nonlinearity                                                    | Measured over any 50 mg interval                                                     |       | ±2               |             | %               |

| Interaxis Alignment Error                                             | , ,                                                                                  |       | ±0.1             |             | Degrees         |

| Cross-Axis Sensitivity <sup>2</sup>                                   |                                                                                      |       | ±1               |             | %               |

| OUTPUT RESOLUTION                                                     | Each axis                                                                            |       |                  |             |                 |

| All g Ranges                                                          | Default resolution                                                                   |       | 10               |             | Bits            |

| ±0.5 <i>g</i> Range                                                   | Full resolution enabled                                                              |       | 10               |             | Bits            |

| ±1 <i>g</i> Range                                                     | Full resolution enabled                                                              |       | 11               |             | Bits            |

| ±2 g Range                                                            | Full resolution enabled                                                              |       | 12               |             | Bits            |

| ±4 g Range                                                            | Full resolution enabled                                                              |       | 13               |             | Bits            |

| SENSITIVITY                                                           | Each axis                                                                            |       | 13               |             | Dits            |

| Sensitivity at X <sub>OUT</sub> , Y <sub>OUT</sub> , Z <sub>OUT</sub> | Any g-range, full resolution mode                                                    |       | 1024             |             | LSB/g           |

| Scholivity at A001, 1001, 2001                                        |                                                                                      | 921   | 1024             | 1126        | _               |

|                                                                       | $\pm 0.5 g$ , 10-bit or full resolution $\pm 1 g$ , 10-bit resolution                | 460   | 512              | 1126<br>563 | LSB/g<br>LSB/g  |

|                                                                       |                                                                                      |       |                  |             | _               |

|                                                                       | ±2 g, 10-bit resolution                                                              | 230   | 256              | 282         | LSB/g           |

|                                                                       | $\pm 4 g$ , 10-bit resolution                                                        | 115   | 128              | 141         | LSB/g           |

| Sensitivity Change Due to Temperature                                 |                                                                                      |       | ±0.01            |             | %/°C            |

| 0 g BIAS LEVEL                                                        | Each axis                                                                            |       |                  |             |                 |

| Initial 0 g Output                                                    | T = 25°С, Хоит, Yоит                                                                 |       | ±50              |             | m <i>g</i>      |

|                                                                       | $T = 25$ °C, $Z_{OUT}$                                                               |       | ±75              |             | m <i>g</i>      |

| 0g Output Drift over Temperature                                      | $-40$ °C < T < $+105$ °C, $X_{OUT}$ , $Y_{OUT}$ , referenced to initial 0 $g$ output | -125  |                  | +125        | m <i>g</i>      |

|                                                                       | -40°C < T < $+105$ °C, Z <sub>OUT</sub> , referenced to initial 0 $g$ output         | -200  |                  | +200        | m <i>g</i>      |

| 0 g Offset Tempco                                                     | Хоит, Үоит                                                                           |       | ±0.5             |             | m <i>g/</i> ℃   |

|                                                                       | Z <sub>OUT</sub>                                                                     |       | ±0.75            |             | m <i>g</i> /℃   |

| NOISE PERFORMANCE                                                     |                                                                                      |       |                  |             |                 |

| Noise Density                                                         | X-, Y-axes                                                                           |       | 150              |             | μ <i>g</i> /√Hz |

|                                                                       | Z-axis                                                                               |       | 250              |             | μ <i>g</i> /√Hz |

| RMS Noise                                                             | X-, Y-axes, 100 Hz output data rate (ODR)                                            |       | 1.5              |             | mg rms          |

|                                                                       | Z-axis, 100 Hz ODR                                                                   |       | 2.5              |             | mg rms          |

| OUTPUT DATA RATE/BANDWIDTH                                            | User selectable                                                                      |       |                  |             |                 |

| Measurement Rate <sup>3</sup>                                         |                                                                                      | 6.25  |                  | 3200        | Hz              |

| SELF TEST⁴                                                            | Data rate ≥ 100 Hz, 2.0 V ≤ $V_S$ ≤ 3.6 V                                            |       |                  |             |                 |

| Output Change in X-Axis                                               |                                                                                      | 0.20  |                  | 2.36        | g               |

| Output Change in Y-Axis                                               |                                                                                      | -2.36 |                  | -0.20       | g               |

| Output Change in Z-Axis                                               |                                                                                      | 0.30  |                  | 3.70        | g               |

| POWER SUPPLY                                                          |                                                                                      |       |                  |             |                 |

| Operating Voltage Range (V <sub>s</sub> )                             |                                                                                      | 2.0   |                  | 3.6         | V               |

| Interface Voltage Range (VDD 1/0)                                     |                                                                                      | 1.7   |                  | Vs          | V               |

| Supply Current                                                        | Data rate > 100 Hz                                                                   | 100   | 170              | 300         | μΑ              |

| · · · · · · · · · · · · · · · · · · ·                                 | Data rate < 10 Hz                                                                    | 30    | 55               | 110         | μΑ              |

| Standby Mode Leakage Current                                          |                                                                                      |       | 0.1              | 2           | μΑ              |

| Turn-On (Wake-Up) Time <sup>5</sup>                                   |                                                                                      |       | 1.4              | -           | ms              |

| TEMPERATURE                                                           |                                                                                      | 1     | 17               |             | 1113            |

| Operating Temperature Range                                           |                                                                                      | -40   |                  | +105        | °C              |

| operating reinperature hange                                          |                                                                                      | -40   |                  | +105        | C               |

$<sup>^{\</sup>mathrm{1}}$  All minimum and maximum specifications are guaranteed. Typical specifications are not guaranteed.

<sup>&</sup>lt;sup>2</sup> Cross-axis sensitivity is defined as coupling between any two axes.

<sup>&</sup>lt;sup>3</sup> Bandwidth is half the output data rate.

<sup>4</sup> Self test change is defined as the output (g) when the SELF\_TEST bit = 1 (in the DATA\_FORMAT register, Address 0x31) minus the output (g) when the SELF\_TEST bit = 0 (in the DATA\_FORMAT register). Due to device filtering, the output reaches its final value after  $4 \times \tau$  when enabling or disabling self test, where  $\tau = 1/(\text{data rate})$ .

<sup>&</sup>lt;sup>5</sup> Turn-on and wake-up times are determined by the user-defined bandwidth. At a 100 Hz data rate, the turn-on and wake-up times are each approximately 11.1 ms. For other data rates, the turn-on and wake-up times are each approximately  $\tau + 1.1$  in milliseconds, where  $\tau = 1/(data rate)$ .

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                         | Rating                                                       |

|---------------------------------------------------|--------------------------------------------------------------|

| Acceleration                                      |                                                              |

| Any Axis, Unpowered                               | 10,000 <i>g</i>                                              |

| Any Axis, Powered                                 | 10,000 <i>g</i>                                              |

| Vs                                                | −0.3 V to +3.9 V                                             |

| V <sub>DD I/O</sub>                               | −0.3 V to +3.9 V                                             |

| All Other Pins                                    | $-0.3$ V to $V_{DD I/O} + 0.3$ V or 3.9 V, whichever is less |

| Output Short-Circuit Duration (Any Pin to Ground) | Indefinite                                                   |

| Temperature Range                                 |                                                              |

| Powered                                           | -40°C to +125°C                                              |

| Storage                                           | -40°C to +125°C                                              |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 3. Thermal Resistance**

| Package Type          | θја   | θις | Unit |

|-----------------------|-------|-----|------|

| 32-Lead LFCSP Package | 27.27 | 30  | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

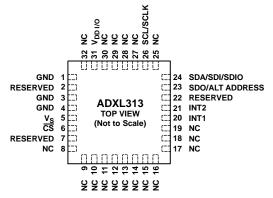

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

- NOTES

1. NC = NO CONNECT. DO NOT CONNECT TO THIS PIN.

2. THE EXPOSED PAD MUST BE SOLDERED TO THE GROUND PLANE.

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.  | Mnemonic            | Description                                                                                          |

|----------|---------------------|------------------------------------------------------------------------------------------------------|

| 1        | GND                 | This pin must be connected to ground.                                                                |

| 2        | RESERVED            | Reserved. This pin must be connected to $V_S$ or left open.                                          |

| 3        | GND                 | This pin must be connected to ground.                                                                |

| 4        | GND                 | This pin must be connected to ground.                                                                |

| 5        | Vs                  | Supply Voltage.                                                                                      |

| 6        | <u>cs</u>           | Chip Select.                                                                                         |

| 7        | RESERVED            | Reserved. This pin must be left open.                                                                |

| 8 to 19  | NC                  | No Connect. Do not connect to this pin.                                                              |

| 20       | INT1                | Interrupt 1 Output.                                                                                  |

| 21       | INT2                | Interrupt 2 Output.                                                                                  |

| 22       | RESERVED            | Reserved. This pin must be connected to GND or left open.                                            |

| 23       | SDO/ALT ADDRESS     | Serial Data Output/Alternate I <sup>2</sup> C Address Select.                                        |

| 24       | SDA/SDI/SDIO        | Serial Data (I <sup>2</sup> C)/Serial Data Input (SPI 4-Wire)/Serial Data Input/Output (SPI 3-Wire). |

| 25       | NC                  | No Connect. Do not connect to this pin.                                                              |

| 26       | SCL/SCLK            | I <sup>2</sup> C Serial Communications Clock/SPI Serial Communications Clock.                        |

| 27 to 30 | NC                  | No Connect. Do not connect to this pin.                                                              |

| 31       | V <sub>DD I/O</sub> | Digital Interface Supply Voltage.                                                                    |

| 32       | NC                  | No Connect. Do not connect to this pin.                                                              |

|          | EP                  | Exposed Pad. The exposed pad must be soldered to the ground plane.                                   |

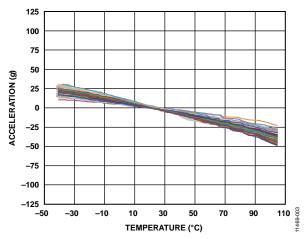

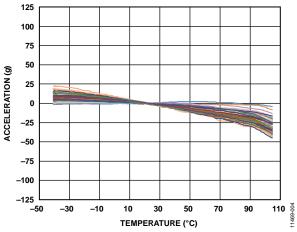

## TYPICAL PERFORMANCE CHARACTERISTICS

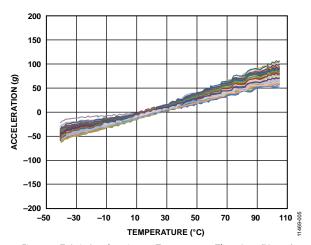

Figure 3. X-Axis Acceleration vs. Temperature, Three Lots (N = 80)

Figure 4. Y-Axis Acceleration vs. Temperature, Three Lots (N = 80)

Figure 5. Z-Axis Acceleration vs. Temperature, Three Lots (N=80)

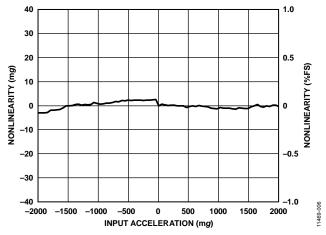

Figure 6. X-Axis Nonlinearity, ±2 g Input Range

Figure 7. Y-Axis Nonlinearity, ±2 g Input Range

Figure 8. Z-Axis Nonlinearity, ±2 g Input Range

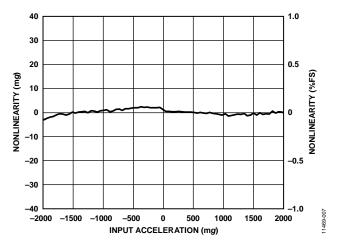

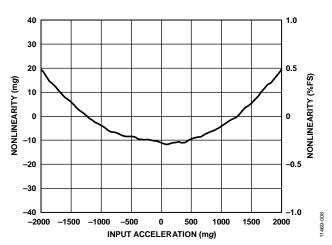

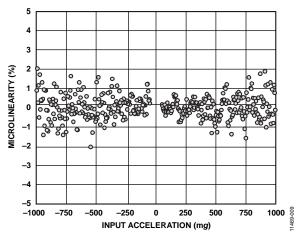

Figure 9. X-Axis Microlinearity, 50 mg Step Size

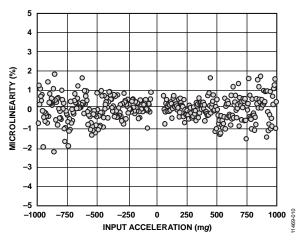

Figure 10. Y-Axis Microlinearity, 50 mg Step Size

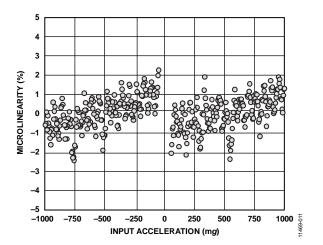

Figure 11. Z-Axis Microlinearity, 50 mg Step Size

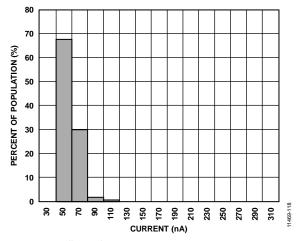

Figure 12. Standby Mode Current Consumption,  $V_S = V_{DD I/O} = 3.3 \text{ V}, 25^{\circ}\text{C}$

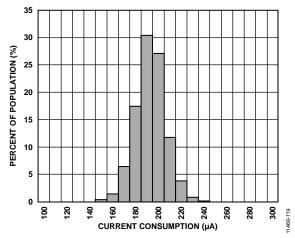

Figure 13. Current Consumption, Measurement Mode, Data Rate = 100 Hz,  $V_S = V_{DD \ VO} = 3.3 \ V, 25 ^{\circ} C$

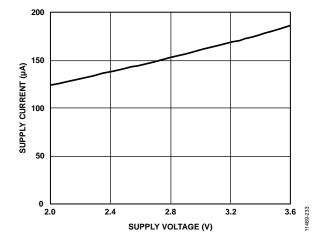

Figure 14. Supply Current vs. Supply Voltage, V₅ at 25°C

### THEORY OF OPERATION

The ADXL313 is a complete 3-axis acceleration measurement system with a selectable measurement range of  $\pm 0.5$  g,  $\pm 1$  g,  $\pm 2$  g, or  $\pm 4$  g. It measures both dynamic acceleration resulting from motion or shock and static acceleration, such as gravity, which allows it to be used as a tilt sensor.

The sensor is a polysilicon surface-micromachined structure built on top of a silicon wafer. Polysilicon springs suspend the structure over the surface of the wafer and provide a resistance against acceleration forces.

Deflection of the structure is measured using differential capacitors that consist of independent fixed plates and plates attached to the moving mass. Acceleration deflects the beam and unbalances the differential capacitor, resulting in a sensor output whose amplitude is proportional to acceleration. Phasesensitive demodulation is used to determine the magnitude and polarity of the acceleration.

### **POWER SEQUENCING**

Power can be applied to  $V_S$  or  $V_{\rm DD\,I/O}$  in any sequence without damaging the ADXL313. All possible power-on modes are summarized in Table 5. The interface voltage level is set with the interface supply voltage,  $V_{\rm DD\,I/O}$ , which must be present to ensure that the ADXL313 does not create a conflict on the communication bus. For single-supply operation,  $V_{\rm DD\,I/O}$  can be the same as the main supply,  $V_S$ . In a dual-supply application, however,  $V_{\rm DD\,I/O}$  can differ from  $V_S$  to accommodate the desired interface voltage, as long as  $V_S$  is greater than or equal to  $V_{\rm DD\,I/O}$ .

After  $V_s$  is applied, the device enters standby mode, where power consumption is minimized and the device waits for  $V_{\rm DD\,I/O}$  to be applied and for the command to enter measurement mode to be received. (This command can be initiated by setting the measure bit in the POWER\_CTL register (Address 0x2D).) In addition, any register can be written to or read from to configure the part while the device is in standby mode. It is recommended that the device be configured in standby mode before measurement mode is enabled. Clearing the measure bit returns the device to the standby mode.

#### **POWER SAVINGS**

#### **Power Modes**

The ADXL313 automatically modulates its power consumption in proportion to its output data rate, as outlined in Table 5. If additional power savings are desired, a lower power mode is available. In this mode, the internal sampling rate is reduced, allowing for power savings in the 12.5 Hz to 400 Hz data rate range at the expense of slightly greater noise. To enter low power mode, set the LOW\_POWER bit (Bit 4) in the BW\_RATE register (Address 0x2C). The current consumption in low power mode is shown in Table 6 for cases where there is an advantage to using low power mode. Use of low power mode for a data rate not shown in Table 6 does not provide any advantage over the same data rate in normal power mode. Therefore, it is recommended that only data rates shown in Table 6 be used in low power mode. The current consumption values shown in Table 5 and Table 6 are for a  $V_{\rm S}$  of 3.3 V.

Table 5. Current Consumption vs. Data Rate  $(T_A = 25^{\circ}C, V_S = V_{DD \text{ } VO} = 3.3 \text{ V})$

| Output Data<br>Rate (Hz) | Bandwidth (Hz) | Rate Code | I <sub>DD</sub> (μA) |

|--------------------------|----------------|-----------|----------------------|

| 3200                     | 1600           | 1111      | 170                  |

| 1600                     | 800            | 1110      | 115                  |

| 800                      | 400            | 1101      | 170                  |

| 400                      | 200            | 1100      | 170                  |

| 200                      | 100            | 1011      | 170                  |

| 100                      | 50             | 1010      | 170                  |

| 50                       | 25             | 1001      | 115                  |

| 25                       | 12.5           | 1000      | 82                   |

| 12.5                     | 6.25           | 0111      | 65                   |

| 6.25                     | 3.125          | 0110      | 57                   |

Table 6. Current Consumption vs. Data Rate, Low Power Mode  $(T_A = 25^{\circ}C, V_S = V_{DD \, I/O} = 3.3 \text{ V})$

| (111 20 0) 19            | 1 DD 1/0 C.C 1 / |           |                      |

|--------------------------|------------------|-----------|----------------------|

| Output Data<br>Rate (Hz) | Bandwidth (Hz)   | Rate Code | I <sub>DD</sub> (μA) |

| 400                      | 200              | 1100      | 115                  |

| 200                      | 100              | 1011      | 82                   |

| 100                      | 50               | 1010      | 65                   |

| 50                       | 25               | 1001      | 57                   |

| 25                       | 12.5             | 1000      | 50                   |

| 12.5                     | 6.25             | 0111      | 43                   |

**Table 7. Power Sequencing**

|                           | 1   | 0                  |                                                                                                                                                                                                              |

|---------------------------|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Condition                 | Vs  | V <sub>DDI/O</sub> | Description                                                                                                                                                                                                  |

| Power Off                 | Off | Off                | The device is completely off, but there is a potential for a communication bus conflict.                                                                                                                     |

| Bus Disabled              | On  | Off                | The device is on in standby mode, but communication is unavailable, and the device creates a conflict on the communication bus. Minimize the duration of this state during power-up to prevent a conflict.   |

| Bus Enabled               | Off | On                 | No functions are available, but the device does not create a conflict on the communication bus.                                                                                                              |

| Standby or<br>Measurement | On  | On                 | The device is in standby mode, awaiting a command to enter measurement mode, and all sensor functions are off. After the device is instructed to enter measurement mode, all sensor functions are available. |

#### Autosleep Mode

Additional power savings can be obtained by having the ADXL313 automatically switch to sleep mode during periods of inactivity. To enable this feature, set the THRESH\_INACT register (Address 0x25) to an acceleration threshold value. Levels of acceleration below this threshold are regarded as no activity. Set TIME\_INACT (Address 0x26) to an appropriate inactivity time period. Then set the AUTO\_SLEEP bit and the link bit in the POWER\_CTL register (Address 0x2D). If the device does not detect a level of acceleration in excess of THRESH\_INACT for TIME\_INACT seconds, the device is transitioned to sleep mode automatically. Current consumption at less than 10 Hz data rates used in this mode is typically 55  $\mu A$  for a  $V_{\rm S}$  of 3.3 V.

#### Standby Mode

For even lower power operation, standby mode can be used. In standby mode, current consumption is reduced to 0.1  $\mu A$  (typical). In this mode, no measurements are made. Standby mode is entered by clearing the measure bit (Bit 3) in the POWER\_CTL register (Address 0x2D). Placing the device into standby mode preserves the contents of the FIFO.

### SERIAL COMMUNICATIONS

I²C and SPI digital communications are available. In both cases, the ADXL313 operates as a slave. I²C mode is enabled if the  $\overline{CS}$  pin is tied high to  $V_{DD\ I\!/O}$ . The  $\overline{CS}$  pin must always be tied high to  $V_{DD\ I\!/O}$  or be driven by an external controller because there is no default mode if the  $\overline{CS}$  pin is left unconnected. Therefore, not taking these precautions may result in an inability to communicate with the part. In SPI mode, the  $\overline{CS}$  pin is controlled by the bus master. In both SPI and I²C modes of operation, ignore data transmitted from the ADXL313 to the master device during writes to the ADXL313.

#### SPI

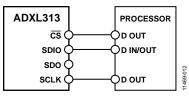

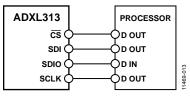

For SPI communication, either 3- or 4-wire configuration is possible, as shown in the connection diagrams in Figure 15 and Figure 16. Clearing the SPI bit in the DATA\_FORMAT register (Address 0x31) selects 4-wire mode, whereas setting the SPI bit selects 3-wire mode. The maximum SPI clock speed is 5 MHz with 100 pF maximum loading, and the timing scheme follows clock polarity (CPOL) = 1 and clock phase (CPHA) = 1. If power is applied to the ADXL313 before the clock polarity and phase of the host processor are configured, the  $\overline{\text{CS}}$  pin must be brought high before changing the clock polarity and phase. When using the 3-wire SPI configuration, it is recommended that the SDO pin be either pulled up to  $V_{\text{DD} \text{ I/O}}$  or pulled down to GND via a 10 k $\Omega$  resistor.

Figure 15. 3-Wire SPI Connection Diagram

Figure 16. 4-Wire SPI Connection Diagram

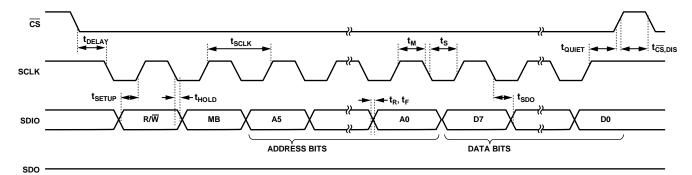

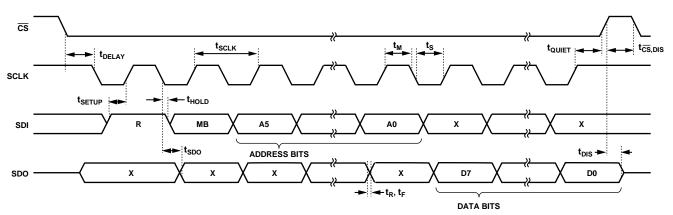

CS is the serial port enable line and is controlled by the SPI master. This line must go low at the start of a transmission and high at the end of a transmission, as shown in Figure 17 to Figure 19. SCLK is the serial port clock and is supplied by the SPI master. SCLK idles high during a period of no transmission. SDI and SDO are the serial data input and output, respectively. Data is updated on the falling edge of SCLK and sampled on the rising edge of SCLK.

To read or write multiple bytes in a single transmission, the multiple-byte bit, located after the R/ $\overline{W}$  bit in the first byte transfer (MB in Figure 17 to Figure 19), must be set. After the register addressing and the first byte of data, each subsequent set of clock pulses (eight clock pulses) causes the ADXL313 to point to the next register for a read or write. This shifting continues until the clock pulses cease and  $\overline{CS}$  is deasserted. To perform reads or writes on different, nonsequential registers,  $\overline{CS}$  must be deasserted between transmissions, and the new register must be addressed separately.

The timing diagram for 3-wire SPI reads or writes is shown in Figure 17. The 4-wire equivalents for SPI reads and writes are shown in Figure 18 and Figure 19, respectively. For correct operation of the part, the logic thresholds and timing parameters in Table 8 and Table 9 must be met at all times.

Use of the 3200 Hz and 1600 Hz output data rates is recommended only with SPI communication rates greater than or equal to 2 MHz. The 800 Hz output data rate is recommended only for communication speeds greater than or equal to 400 kHz, and the remaining data rates scale proportionally. For example, the minimum recommended communication speed for a 200 Hz output data rate is  $100 \, \text{kHz}$ . Operation at an output data rate below the recommended minimum may result in undesirable effects on the acceleration data, including missing samples or additional noise.

**Table 8. SPI Digital Input/Output**

|                                              |                                                  |                        | Limit <sup>1</sup>      |      |

|----------------------------------------------|--------------------------------------------------|------------------------|-------------------------|------|

| Parameter                                    | Test Conditions/Comments                         | Min                    | Max                     | Unit |

| Digital Input                                |                                                  |                        |                         |      |

| Low Level Input Voltage (V <sub>IL</sub> )   |                                                  |                        | $0.3 \times V_{DD I/O}$ | V    |

| High Level Input Voltage (V <sub>IH</sub> )  |                                                  | $0.7 \times V_{DDI/O}$ |                         | V    |

| Low Level Input Current (I <sub>IL</sub> )   | $V_{IN} = V_{DD\ I/O}$                           |                        | 0.1                     | μΑ   |

| High Level Input Current (I <sub>IH</sub> )  | $V_{IN} = 0 V$                                   | -0.1                   |                         | μΑ   |

| Digital Output                               |                                                  |                        |                         |      |

| Low Level Output Voltage (Vol)               | $I_{OL} = 10 \text{ mA}$                         |                        | $0.2 \times V_{DD I/O}$ | V    |

| High Level Output Voltage (Vон)              | $I_{OH} = -4 \text{ mA}$                         | $0.8 \times V_{DDI/O}$ |                         | V    |

| Low Level Output Current (IoL)               | $V_{OL} = V_{OL, max}$                           | 10                     |                         | mA   |

| High Level Output Current (I <sub>OH</sub> ) | $V_{OH} = V_{OH,min}$                            |                        | -4                      | mA   |

| Pin Capacitance                              | $f_{IN} = 1 \text{ MHz}, V_{IN} = 2.5 \text{ V}$ |                        | 8                       | рF   |

<sup>&</sup>lt;sup>1</sup> Limits based on characterization results; not production tested.

Table 9. SPI Timing  $(T_A = 25^{\circ}C, V_S = V_{DD I/O} = 3.3 V)^{1}$

|                             | Lim                   | it <sup>2, 3</sup> |      |                                                                                |

|-----------------------------|-----------------------|--------------------|------|--------------------------------------------------------------------------------|

| Parameter                   | Min                   | Max                | Unit | Description                                                                    |

| f <sub>SCLK</sub>           |                       | 5                  | MHz  | SPI clock frequency.                                                           |

| <b>t</b> sclk               | 200                   |                    | ns   | 1/(SPI clock frequency) mark-space ratio for the SCLK input is 40/60 to 60/40. |

| t <sub>DELAY</sub>          | 5                     |                    | ns   | CS falling edge to SCLK falling edge.                                          |

| <b>t</b> <sub>QUIET</sub>   | 5                     |                    | ns   | SCLK rising edge to $\overline{\text{CS}}$ rising edge.                        |

| t <sub>DIS</sub>            |                       | 10                 | ns   | CS rising edge to SDO disabled.                                                |

| t <sub>CS</sub> ,DIS        | 150                   |                    | ns   | CS deassertion between SPI communications.                                     |

| <b>t</b> s                  | $0.3 \times t_{SCLK}$ |                    | ns   | SCLK low pulse width (space).                                                  |

| t <sub>M</sub>              | $0.3 \times t_{SCLK}$ |                    | ns   | SCLK high pulse width (mark).                                                  |

| t <sub>SETUP</sub>          | 5                     |                    | ns   | SDI valid before SCLK rising edge.                                             |

| t <sub>HOLD</sub>           | 5                     |                    | ns   | SDI valid after SCLK rising edge.                                              |

| t <sub>SDO</sub>            |                       | 40                 | ns   | SCLK falling edge to SDO/SDIO output transition.                               |

| t <sub>R</sub> 4            |                       | 20                 | ns   | SDO/SDIO output high to output low transition.                                 |

| t <sub>F</sub> <sup>4</sup> |                       | 20                 | ns   | SDO/SDIO output low to output high transition.                                 |

$<sup>^{1}</sup>$  The  $\overline{\text{CS}}$ , SCLK, SDI, and SDO pins are not internally pulled up or down; they must be driven for proper operation.  $^{2}$  Limits based on characterization results, characterized with  $f_{\text{SCLK}} = 5$  MHz and bus load capacitance of 100 pF; not production tested.

<sup>&</sup>lt;sup>3</sup> The timing values are measured corresponding to the input thresholds ( $V_{IL}$  and  $V_{H}$ ) given in Table 8.

<sup>&</sup>lt;sup>4</sup> Output rise and fall times measured with capacitive load of 150 pF.

NOTES 1.  $t_{\rm SDO}$  IS ONLY PRESENT DURING READS.

Figure 17. SPI 3-Wire Read/Write

11469-014

Figure 18. SPI 4-Wire Read

Figure 19. SPI 4-Wire Write

#### I<sup>2</sup>C

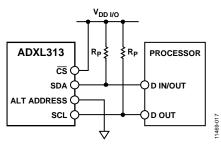

With  $\overline{CS}$  tied high to  $V_{DD I/O}$ , the ADXL313 is in  $I^2C$  mode, requiring a simple 2-wire connection, as shown in Figure 20. The ADXL313 conforms to the UM10204 I<sup>2</sup>C-Bus Specification and User Manual, Rev. 03-19 June 2007, available from NXP Semiconductor. It supports standard (100 kHz) and fast (400 kHz) data transfer modes if the bus parameters given in Table 10 and Table 11 are met. Single- or multiple-byte reads/writes are supported, as shown in Figure 21. With the ALT ADDRESS pin high, the 7-bit I<sup>2</sup>C address for the device is 0x1D, followed by the  $R/\overline{W}$  bit. This translates to 0x3A for a write and 0x3B for a read. An alternate I<sup>2</sup>C address of 0x53 (followed by the R/W bit) can be chosen by grounding the ALT ADDRESS pin (Pin 23). This translates to 0xA6 for a write and 0xA7 for a read.

Figure 20. I<sup>2</sup>C Connection Diagram (Address 0x53)

If other devices are connected to the same I<sup>2</sup>C bus, the nominal operating voltage level of these other devices cannot exceed  $V_{\text{DD}\,\text{I/O}}$ by more than 0.3 V. External pull-up resistors, R<sub>P</sub>, are necessary for proper I<sup>2</sup>C operation. To ensure proper operation, refer to the UM10204 I<sup>2</sup>C-Bus Specification and User Manual, Rev. 03— 19 June 2007, when selecting pull-up resistor values.

Table 10. I<sup>2</sup>C Digital Input/Output

|                                             |                                                  |                         | Limit <sup>1</sup>        |      |

|---------------------------------------------|--------------------------------------------------|-------------------------|---------------------------|------|

| Parameter                                   | Test Conditions/Comments                         | Min                     | Max                       | Unit |

| Digital Input                               |                                                  |                         |                           |      |

| Low Level Input Voltage (V <sub>I</sub> L)  |                                                  |                         | 0.3 × V <sub>DD I/O</sub> | V    |

| High Level Input Voltage (V <sub>IH</sub> ) |                                                  | $0.7 \times V_{DD I/O}$ |                           | V    |

| Low Level Input Current (I⊥)                | $V_{IN} = V_{DD I/O}$                            |                         | 0.1                       | μΑ   |

| High Level Input Current (I <sub>H</sub> )  | $V_{IN} = 0 V$                                   | -0.1                    |                           | μΑ   |

| Digital Output                              |                                                  |                         |                           |      |

| Low Level Output Voltage (V <sub>OL</sub> ) | $V_{DD I/O} < 2 V$ , $I_{OL} = 3 \text{ mA}$     |                         | $0.2 \times V_{DD I/O}$   | V    |

|                                             | $V_{DD I/O} \ge 2 V$ , $I_{OL} = 3 \text{ mA}$   |                         | 400                       | mV   |

| Low Level Output Current (IoL)              | $V_{OL} = V_{OL, max}$                           | 3                       |                           | mA   |

| Pin Capacitance                             | $f_{IN} = 1 \text{ MHz}, V_{IN} = 2.5 \text{ V}$ |                         | 8                         | pF   |

<sup>&</sup>lt;sup>1</sup> Limits based on characterization results; not production tested.

| SINGLE-BY | TE WRITE            |                       |     |                  |     |                    |               |      |      |    |      |     |      |        |      |      |      |

|-----------|---------------------|-----------------------|-----|------------------|-----|--------------------|---------------|------|------|----|------|-----|------|--------|------|------|------|

| MASTER    | START               | SLAVE ADDRESS + WRITE |     | REGISTER ADDRESS |     |                    | DATA          |      | STOP |    |      |     |      |        |      |      |      |

| SLAVE     |                     |                       | ACK |                  | ACK |                    |               | ACK  |      |    |      |     |      |        |      |      |      |

|           |                     |                       |     |                  |     |                    |               |      |      |    |      |     |      |        |      |      |      |

| MULTIPLE- | MULTIPLE-BYTE WRITE |                       |     |                  |     |                    |               |      |      |    |      |     |      |        |      |      |      |

| MASTER    | START               | SLAVE ADDRESS + WRITE |     | REGISTER ADDRESS |     |                    | DATA          |      |      | DA | ATA  |     | STOP |        |      |      |      |

| SLAVE     |                     |                       | ACK |                  | ACK |                    |               | ACK  |      |    |      | ACK |      |        |      |      |      |

|           |                     |                       |     |                  |     |                    | •             |      |      |    |      |     |      |        |      |      |      |

| SINGLE-BY | TE READ             |                       |     |                  |     |                    |               |      |      |    |      |     |      |        |      |      |      |

| MASTER    | START               | SLAVE ADDRESS + WRITE |     | REGISTER ADDRESS |     | START <sup>1</sup> | SLAVE ADDRESS | READ |      |    |      |     | NAC  | K STOP |      |      |      |

| SLAVE     |                     |                       | ACK |                  | ACK |                    |               |      | ACK  |    | DATA |     |      |        |      |      |      |

|           |                     |                       |     |                  |     |                    |               |      |      |    |      |     |      |        |      |      |      |

| MULTIPLE- | MULTIPLE-BYTE READ  |                       |     |                  |     |                    |               |      |      |    |      |     |      |        |      |      |      |

| MASTER    | START               | SLAVE ADDRESS + WRITE |     | REGISTER ADDRESS |     | START <sup>1</sup> | SLAVE ADDRESS | READ |      |    |      |     | AC   | К      |      | NACK | STOP |

| SLAVE     |                     |                       | ACK |                  | ACK |                    |               |      | ACK  |    | DATA |     |      |        | DATA |      |      |

1. THIS START IS EITHER A RESTART OR A STOP FOLLOWED BY A START.

2. THE SHADED AREAS REPRESENT WHEN THE DEVICE IS LISTENING.

Figure 21. I<sup>2</sup>C Device Addressing

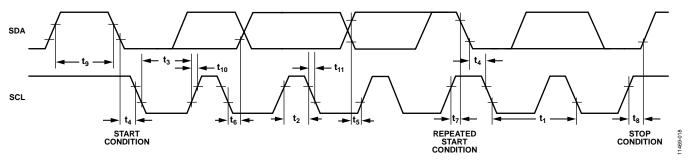

Table 11. I<sup>2</sup>C Timing ( $T_A = 25^{\circ}C$ ,  $V_S = V_{DD I/O} = 3.3 V$ )

|                                      | Lim               | nit <sup>1, 2</sup> |      |                                                              |

|--------------------------------------|-------------------|---------------------|------|--------------------------------------------------------------|

| Parameter                            | Min               | Max                 | Unit | Description                                                  |

| f <sub>SCL</sub>                     |                   | 400                 | kHz  | SCL clock frequency                                          |

| $t_1$                                | 2.5               |                     | μs   | SCL cycle time                                               |

| $t_2$                                | 0.6               |                     | μs   | SCL high time                                                |

| t <sub>3</sub>                       | 1.3               |                     | μs   | SCL low time                                                 |

| t <sub>4</sub>                       | 0.6               |                     | μs   | Start/repeated start condition hold time                     |

| <b>t</b> <sub>5</sub>                | 100               |                     | ns   | Data setup time                                              |

| t <sub>6</sub> <sup>3, 4, 5, 6</sup> | 0                 | 0.9                 | μs   | Data hold time                                               |

| $t_7$                                | 0.6               |                     | μs   | Setup time for repeated start                                |

| t <sub>8</sub>                       | 0.6               |                     | μs   | Stop condition setup time                                    |

| t <sub>9</sub>                       | 1.3               |                     | μs   | Bus-free time between a stop condition and a start condition |

| t <sub>10</sub>                      |                   | 300                 | ns   | Rise time of both SCL and SDA when receiving                 |

|                                      | 0                 |                     | ns   | Rise time of both SCL and SDA when receiving or transmitting |

| t <sub>11</sub>                      |                   | 250                 | ns   | Fall time of SDA when receiving                              |

|                                      |                   | 300                 | ns   | Fall time of both SCL and SDA when transmitting              |

|                                      | $20 + 0.1  C_b^7$ |                     | ns   | Fall time of both SCL and SDA when transmitting or receiving |

| C <sub>b</sub>                       |                   | 400                 | pF   | Capacitive load for each bus line                            |

$<sup>^{1}</sup>$  Limits based on characterization results, with  $f_{SCL} = 400 \text{ kHz}$  and a 3 mA sink current; not production tested.

<sup>&</sup>lt;sup>7</sup> C<sub>b</sub> is the total capacitance of one bus line in picofarads.

Figure 22. I<sup>2</sup>C Timing Diagram

$<sup>^2</sup>$  All values referred to the  $V_{\text{IH}}$  and the  $V_{\text{IL}}$  levels given in Table 10.

<sup>&</sup>lt;sup>3</sup> t<sub>c</sub> is the data hold time that is measured from the falling edge of SCL. It applies to data in transmission and acknowledge.

<sup>4</sup> A transmitting device must internally provide an output hold time of at least 300 ns for the SDA signal (with respect to V<sub>IH, min</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

<sup>&</sup>lt;sup>5</sup> The maximum t<sub>6</sub> value must be met only if the device does not stretch the low period (t<sub>3</sub>) of the SCL signal.

<sup>&</sup>lt;sup>6</sup> The maximum value for t<sub>6</sub> is a function of the clock low time (t<sub>3</sub>), the clock rise time (t<sub>10</sub>), and the minimum data setup time (t<sub>5(min)</sub>). This value is calculated as  $t_{6(max)} = t_3 - t_{10} - t_{5(min)}$

#### **INTERRUPTS**

The ADXL313 provides two output pins for driving interrupts: INT1 and INT2. Both interrupt pins are push-pull, low impedance pins with output specifications shown in Table 12. The default configuration of the interrupt pins is active high. This can be changed to active low by setting the INT\_INVERT bit in the DATA\_FORMAT register (Address 0x31). All functions can be used simultaneously, with the only limiting feature being that some functions may need to share interrupt pins.

Interrupts are enabled by setting the appropriate bit in the INT\_ENABLE register (Address 0x2E) and are mapped to either the INT1 or INT2 pin based on the contents of the INT\_MAP register (Address 0x2F). When initially configuring the interrupt pins, it is recommended that the functions and interrupt mapping be completed before enabling the interrupts. When changing the configuration of an interrupt, it is recommended that the interrupt be disabled first, by clearing the bit corresponding to that function in the INT\_ENABLE register, and then the function be reconfigured before enabling the interrupt again. Configuration of the functions while the interrupts are disabled helps to prevent the accidental generation of an interrupt.

The interrupt functions are latched and cleared either by reading the data registers (Address 0x32 to Address 0x37) until the interrupt condition is no longer valid for the data-related interrupts or by reading the INT\_SOURCE register (Address 0x30) for the remaining interrupts. The following sections describe the interrupts that can be set in the INT\_ENABLE register and monitored in the INT\_SOURCE register.

#### DATA READY

The DATA\_READY bit is set when new data is available and is cleared when no new data is available.

#### Activity

The activity bit is set when acceleration greater than the value stored in the THRESH\_ACT register (Address 0x24) is sensed.

#### **Inactivity**

The inactivity bit is set when acceleration of less than the value stored in the THRESH\_INACT register (Address 0x25) is sensed for more time than is specified in the TIME\_INACT register (Address 0x26). The maximum value for TIME\_INACT is 255 sec.

#### Watermark

The watermark bit is set when the number of samples in the FIFO equals the value stored in the samples bits in the FIFO\_CTL register (Address 0x38). The watermark bit is cleared automatically when the FIFO is read, and the content returns to a value below the value stored in the samples bits.

#### Overrun

The overrun bit is set when new data replaces unread data. The precise operation of the overrun function depends on the FIFO mode. In bypass mode, the overrun bit is set when new data replaces unread data in the DATA\_Xx, DATA\_Yx, and DATA\_Zx registers (Address 0x32 to Address 0x37). In all other modes, the overrun bit is set when the FIFO is filled. The overrun bit is automatically cleared when the contents of FIFO are read.

#### **FIFO**

The ADXL313 contains patent pending technology for an embedded memory management system with a 32-level FIFO that can be used to minimize host processor burden. This buffer has four modes: bypass, FIFO, stream, and trigger (see Table 17). Each mode is selected by the settings of the FIFO\_MODE bits in the FIFO\_CTL register (Address 0x38).

#### **Bypass Mode**

In bypass mode, the FIFO is not operational and, therefore, remains empty.

Table 12. Interrupt Pin Digital Output

|                                          |                                                  |                         | Limit <sup>1</sup>      |      |

|------------------------------------------|--------------------------------------------------|-------------------------|-------------------------|------|

| Parameter                                | Test Conditions/Comments                         | Min                     | Max                     | Unit |

| Digital Output                           |                                                  |                         |                         |      |

| Low Level Output Voltage (Vol)           | $I_{OL} = 300  \mu A$                            |                         | $0.2 \times V_{DD I/O}$ | V    |

| High Level Output Voltage (Voн)          | $I_{OH} = -150 \mu A$                            | $0.8 \times V_{DD I/O}$ |                         | V    |

| Low Level Output Current (IoL)           | $V_{OL} = V_{OL, max}$                           | 300                     |                         | μΑ   |

| High Level Output Current (IoH)          | $V_{OH} = V_{OH, min}$                           |                         | -150                    | μΑ   |

| Pin Capacitance                          | $f_{IN} = 1 \text{ MHz}, V_{IN} = 2.5 \text{ V}$ |                         | 8                       | pF   |

| Rise/Fall Time                           |                                                  |                         |                         |      |

| Rise Time (t <sub>R</sub> ) <sup>2</sup> | C <sub>LOAD</sub> = 150 pF                       |                         | 210                     | ns   |

| Fall Time (t <sub>F</sub> ) <sup>3</sup> | C <sub>LOAD</sub> = 150 pF                       |                         | 150                     | ns   |

<sup>&</sup>lt;sup>1</sup> Limits based on characterization results, not production tested.

$<sup>^2</sup>$  Rise time is measured as the transition time from  $V_{OL,\,max}$  to  $V_{OH,\,min}$  of the INTx pin.

$<sup>^3</sup>$  Fall time is measured as the transition time from  $V_{\text{OH, min}}$  to  $V_{\text{OL, max}}$  of the INTx pin.

#### FIFO Mode

In FIFO mode, data from measurements of the x-, y-, and z-axes are stored in the FIFO. When the number of samples in the FIFO equals the level specified in the samples bits of the FIFO\_CTL register (Address 0x38), the watermark interrupt is set. The FIFO continues accumulating samples until it is full (32 samples from measurements of the x-, y-, and z-axes) and then stops collecting data. After the FIFO stops collecting data, the device continues to operate; therefore, features such as activity detection can be used after the FIFO is full. The watermark interrupt continues to occur until the number of samples in the FIFO is less than the value stored in the samples bits of the FIFO\_CTL register.

#### Stream Mode

In stream mode, data from measurements of the x-, y-, and z-axes is stored in FIFO. When the number of samples in the FIFO equals the level specified in the samples bits of the FIFO\_CTL register (Address 0x38), the watermark interrupt is set. FIFO continues accumulating samples and holds the latest 32 samples from measurements of the x-, y-, and z-axes, discarding older data as new data arrives. The watermark interrupt continues occurring until the number of samples in FIFO is less than the value stored in the samples bits of the FIFO\_CTL register.

#### Trigger Mode

In trigger mode, the FIFO accumulates samples, holding the latest 32 samples from measurements of the x-, y-, and z-axes. After a trigger event occurs and an interrupt is sent to the INT1 or INT2 pin (determined by the trigger bit in the FIFO\_CTL register), FIFO keeps the last n samples (where n is the value specified by the samples bits in the FIFO\_CTL register) and then operates in FIFO mode, collecting new samples only when the FIFO is not full. A delay of at least 5  $\mu$ s must be present between the trigger event occurring and the start of reading data from the FIFO to allow the FIFO to discard and retain the necessary samples. Additional trigger events cannot be recognized until the trigger mode is reset. To reset the trigger mode, set the device to bypass mode and then set the device back to trigger mode. Note that the FIFO data must be read first because placing the device into bypass mode clears FIFO.

#### **Retrieving Data from FIFO**

The FIFO data is read through the DATA\_Xx, DATA\_Yx, and DATA\_Zx registers (Address 0x32 to Address 0x37). When the FIFO is in FIFO, stream, or trigger mode, reads to the DATA\_Xx, DATA\_xY, and DATA\_Zx registers read data stored in the FIFO. Each time data is read from the FIFO, the oldest x-, y-, and z-axes data is placed into the DATA\_Xx, DATA\_Yx, and DATA\_Zx registers.

If a single-byte read operation is performed, the remaining bytes of data for the current FIFO sample are lost. Therefore, all axes of interest must be read in a burst (or multiple-byte) read operation. To ensure that the FIFO has completely popped (that is, that new data has completely moved into the DATA\_Xx, DATA\_Yx, and DATA\_Zx registers), there must be at least 5  $\mu s$  between the end of reading the data registers and the start of a new read of the FIFO or a read of the FIFO\_STATUS register (Address 0x39). The end of reading a data register is signified by the transition from Register 0x37 to Register 0x38 or by the  $\overline{CS}$  pin going high.

For SPI operation at 1.6 MHz or less, the register addressing portion of the transmission is a sufficient delay to ensure that the FIFO has completely popped. For SPI operation greater than 1.6 MHz, it is necessary to deassert the  $\overline{CS}$  pin to ensure a total delay of 5  $\mu$ s; otherwise, the delay is not sufficient. The total delay necessary for 5 MHz operation is at most 3.4  $\mu$ s. This is not a concern when using I<sup>2</sup>C mode because the communication rate is low enough to ensure a sufficient delay between FIFO reads.

#### **SELF TEST**

The ADXL313 incorporates a self test feature that effectively tests its mechanical and electronic systems simultaneously. When the self test function is enabled (via the SELF\_TEST bit in the DATA\_FORMAT register, Address 0x31), an electrostatic force is exerted on the mechanical sensor. This electrostatic force moves the mechanical sensing element in the same manner as acceleration, and it is additive to the acceleration experienced by the device. This added electrostatic force results in an output change in the x-, y-, and z-axes. Because the electrostatic force is proportional to Vs<sup>2</sup>, the output change varies with Vs. The self test feature of the ADXL313 also exhibits a bimodal behavior. However, the limits shown in Table 1 and Table 13 are valid for all potential self test values across the entire allowable voltage range. Use of the self test feature at data rates of less than 100 Hz or at 1600 Hz may yield values outside these limits. Therefore, the part must be in normal power operation (LOW\_POWER bit = 0 in the BW RATE register, Address 0x2C) and be placed into a data rate of 100 Hz through 800 Hz or 3200 Hz for the self test function to operate correctly.

Table 13. Self Test Output ( $T_A = 25^{\circ}C$ , 2.0  $V \le V_S \le 3.6 V$ )

| Axis | Min ( <i>g</i> ) | Max ( <i>g</i> ) |  |

|------|------------------|------------------|--|

| Χ    | 0.20             | 2.36             |  |

| Υ    | -2.36            | +0.20            |  |

| Z    | 0.30             | 3.70             |  |

## **REGISTER MAP**

Table 14. Register Map

| Reg             | Name          | Туре | D7             | D6              | D5             | D4                 | D3              | D2         | D1        | D0      | Reset<br>Value |  |

|-----------------|---------------|------|----------------|-----------------|----------------|--------------------|-----------------|------------|-----------|---------|----------------|--|

| 0x00            | DEVID_0       | R    |                |                 |                | DEVID <sub>.</sub> | _0[7:0]         |            |           |         | 0xAD           |  |

| 0x01            | DEVID_1       | R    |                |                 |                | DEVID <sub>.</sub> | _1[7:0]         |            |           |         | 0x1D           |  |

| 0x02            | PARTID        | R    |                |                 |                | PARTI              | D[7:0]          |            |           |         | 0xDC           |  |

| 0x03            | REVID         | R    |                |                 |                | REVIE              | D[7:0]          |            |           |         | 0x00           |  |

| 0x04            | XID           | R    |                |                 |                | XID[               | [7:0]           |            |           |         | 0x00           |  |

| 0x05 to<br>0x17 | Reserved      | RSVD |                |                 |                | Rese               | rved            |            |           |         |                |  |

| 0x18            | SOFT_RESET    | R/W  |                |                 |                | SOFT_RE            | SET[7:0]        |            |           |         | 0x00           |  |

| 0x19 to<br>0x1D | Reserved      | RSVD |                |                 |                | Rese               | rved            |            |           |         |                |  |

| 0x1E            | OFSX          | R/W  |                |                 |                | OFSX               | ([7:0]          |            |           |         | 0x00           |  |

| 0x1F            | OFSY          | R/W  |                |                 |                | OFSY               | /[7:0]          |            |           |         | 0x00           |  |

| 0x20            | OFSZ          | R/W  |                |                 |                | OFSZ               | <u>Z</u> [7:0]  |            |           |         | 0x00           |  |

| 0x21 to<br>0x23 | Reserved      | RSVD |                |                 |                | Rese               | rved            |            |           |         |                |  |

| 0x24            | THRESH_ACT    | R/W  |                |                 |                | THRESH_            | _ACT[7:0]       |            |           |         | 0x00           |  |

| 0x25            | THRESH_INACT  | R/W  |                |                 |                | THRESH_I           |                 |            |           |         | 0x00           |  |

| 0x26            | TIME_INACT    | R/W  |                |                 |                | TIME_IN            | ACT[7:0]        | ACT[7:0]   |           |         |                |  |

| 0x27            | ACT_INACT_CTL | R/W  | ACT_<br>AC/DC  | ACT_X           | ACT_Y          | ACT_Z              | INACT_<br>AC/DC | INACT_X    | INACT_Y   | INACT_Z | 0x00           |  |

| 0x28 to<br>0x2B | Reserved      | RSVD |                | l               |                | Rese               |                 |            |           | l       |                |  |

| 0x2C            | BW_RATE       | R/W  | 0              | 0               | 0              | LOW_POWER          |                 | Rat        | e[3:0]    |         | 0x0A           |  |

| 0x2D            | POWER_CTL     | R/W  | 0              | I2C_<br>DISABLE | Link           | AUTO_SLEEP         | Measure         | Sleep      | Wake-u    | p[1:0]  | 0x00           |  |

| 0x2E            | INT_ENABLE    | R/W  | DATA_<br>READY | 0               | 0              | Activity           | Inactivity      | 0          | Watermark | Overrun | 0x00           |  |

| 0x2F            | INT_MAP       | R/W  | DATA_<br>READY | 0               | 0              | Activity           | Inactivity      | 0          | Watermark | Overrun | 0x00           |  |

| 0x30            | INT_SOURCE    | R    | DATA_<br>READY | 0               | 0              | Activity           | Inactivity      | 0          | Watermark | Overrun | 0x02           |  |

| 0x31            | DATA_FORMAT   | R/W  | SELF_<br>TEST  | SPI             | INT_<br>INVERT | 0                  | FULL_RES        | Justify    | Range     | [1:0]   | 0x00           |  |

| 0x32            | DATA_X0       | R    |                |                 |                | DATA_              | X0[7:0]         |            | 1         |         | 0x00           |  |

| 0x33            | DATA_X1       | R    |                |                 |                | DATA_              | X1[7:0]         |            |           |         | 0x00           |  |

| 0x34            | DATA_Y0       | R    |                |                 |                | DATA_              | Y0[7:0]         |            |           |         | 0x00           |  |

| 0x35            | DATA_Y1       | R    |                |                 |                | DATA_              | Y1[7:0]         |            |           |         | 0x00           |  |

| 0x36            | DATA_Z0       | R    |                | DATA_Z0[7:0]    |                |                    |                 |            |           |         | 0x00           |  |

| 0x37            | DATA_Z1       | R    |                | DATA_Z1[7:0]    |                |                    |                 |            |           |         | 0x00           |  |

| 0x38            | FIFO_CTL      | R/W  | FIFO_MC        | DE[1:0]         | Trigger        |                    | Sa              | mples[4:0] |           |         | 0x00           |  |

| 0x39            | FIFO_STATUS   | R    | FIFO_TRIG      | 0               |                | 1                  | Entr            | ies        |           |         | 0x00           |  |

#### **REGISTER DEFINITIONS**

#### Register 0x00—DEVID\_0 (Read Only)

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  |

The DEVID\_0 register holds a fixed device ID identifying Analog Devices, Inc., as the device manufacturer. The default value of this register is 0xAD.

Register 0x01—DEVID\_1 (Read Only)

| D7 | D6 |   | D4 |   | D2 | D1 | D0 |

|----|----|---|----|---|----|----|----|

| 0  | 0  | 0 | 1  | 1 | 1  | 0  | 1  |

The DEVID\_1 register holds a fixed device ID that further enhances traceability of the ADXL313. The default value of this register is 0x1D.

Register 0x02—PARTID (Read Only)

| Ī | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|----|----|----|----|----|----|----|----|

| Ī | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 1  |

The PARTID register identifies the device as an ADXL313. The default hexadecimal value stored in this register, 0xDC, is meant to be interpreted as an octal value that corresponds to 313. If the user does not read back 0xDC from this register, assume that the device under test is not an ADXL313 device.

Register 0x03—REVID (Read Only)

| D7 | D6 | D5                                                       | D4 | D3 | D2 | D1 | D0 |

|----|----|----------------------------------------------------------|----|----|----|----|----|

|    |    | D5         D4         D3         D2           REVID[7:0] |    |    |    |    |    |

The number contained in the REVID register represents the silicon revision of the ADXL313. This number is incremented for any major silicon revision.

Register 0x04—XID (Read Only)

|    | -  |    |     | - //  | I _ | _  | _  |

|----|----|----|-----|-------|-----|----|----|

| D7 | D6 | D5 | D4  | D3    | D2  | D1 | D0 |

|    |    |    | XID | [7:0] |     |    |    |

The XID register stores a semi-unique serial number that is generated from the device trim and calibration process.

Reaister 0x18—SOFT RESET (Read/Write)

| negisi | hegister 0x18—30F1_hE3E1 (hedd/Write) |    |         |          |    |    |    |  |  |  |  |  |

|--------|---------------------------------------|----|---------|----------|----|----|----|--|--|--|--|--|

| D7     | D6                                    | D5 | D4      | D3       | D2 | D1 | D0 |  |  |  |  |  |

|        |                                       |    | SOFT RE | SET[7:0] |    |    |    |  |  |  |  |  |

Writing a value of 0x52 to Register 0x18 triggers the soft reset function of the ADXL313. The soft reset returns the ADXL313 to the beginning of its power-on initialization routine, clearing the configuration settings that were written to the memory map, which allows easy reconfiguration of the ADXL313 device.

Register 0x1E—OFSX (Read/Write), Register 0x1F—OFSY (Read/Write), Register 0x20—OFSZ (Read/Write)

| D7 | D6        | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

|----|-----------|----|----|----|----|----|----|--|--|--|

|    | OFSX[7:0] |    |    |    |    |    |    |  |  |  |

|    | OFSY[7:0] |    |    |    |    |    |    |  |  |  |

|    | OFSZ[7:0] |    |    |    |    |    |    |  |  |  |

The OFSX, OFSY, and OFSZ registers are each eight bits and offer user-set offset adjustments in twos complement format with a scale factor of 3.9 mg/LSB (that is, 0x7F = 0.5 g). The value stored in the offset registers is automatically added to the acceleration data, and the resulting value is stored in the output data registers.

Register 0x24—THRESH\_ACT (Read/Write)

| D7              | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-----------------|----|----|----|----|----|----|----|

| THRESH_ACT[7:0] |    |    |    |    |    |    |    |

The THRESH\_ACT register is eight bits and holds the threshold value for detecting activity. The data format is unsigned; therefore, the magnitude of the activity event is compared with the value in the THRESH\_ACT register. The scale factor is 15.625 mg/LSB. A value of 0 may result in undesirable behavior if the activity interrupt is enabled.

Register 0x25—THRESH\_INACT (Read/Write)

| D7 | D6 | D5 | D4      | D3       | D2 | D1 | D0 |

|----|----|----|---------|----------|----|----|----|

|    |    | Т  | HRESH_I | NACT[7:0 | 0] |    |    |

The THRESH\_INACT register is eight bits and holds the threshold value for detecting inactivity. The data format is unsigned; therefore, the magnitude of the inactivity event is compared with the value in the THRESH\_INACT register. The scale factor is 15.625 mg/LSB. A value of 0 may result in undesirable behavior if the inactivity interrupt is enabled.

Register 0x26—TIME INACT (Read/Write)

| D7 | D6              | D5 | D4 | D3 | D2 | D1 | D0 |

|----|-----------------|----|----|----|----|----|----|

|    | TIME_INACT[7:0] |    |    |    |    |    |    |

The TIME\_INACT register is eight bits and contains an unsigned time value. Acceleration must be less than the value in the THRESH\_INACT register for the amount of time represented by TIME\_INACT for inactivity to be declared. The scale factor is 1 sec/LSB. Unlike the other interrupt functions, which use unfiltered data (see the Threshold section), the inactivity function uses filtered output data. At least one output sample must be generated for the inactivity interrupt to be triggered. This results in the function appearing unresponsive if the TIME\_INACT register is set to a value less than the time constant of the output data rate. A value of 0 results in an interrupt when the output data is less than the value in the THRESH\_INACT register.

Register 0x27—ACT\_INACT\_CTL (Read/Write)

| D7          | D6      | D5      | D4      |

|-------------|---------|---------|---------|

| ACT_AC/DC   | ACT_X   | ACT_Y   | ACT_Z   |

| D3          | D2      | D1      | D0      |

| INACT_AC/DC | INACT_X | INACT_Y | INACT_Z |

#### ACT\_AC/DC and INACT\_AC/DC Bits

A setting of 0 selects dc-coupled operation, and a setting of 1 enables ac-coupled operation. In dc-coupled operation, the current acceleration magnitude is compared directly with THRESH\_ACT and THRESH\_INACT to determine whether activity or inactivity is detected.

In ac-coupled operation for activity detection, the acceleration value at the start of activity detection is taken as a reference value. New samples of acceleration are then compared to this reference value and, if the magnitude of the difference exceeds the THRESH\_ACT value, the device triggers an activity interrupt.

Similarly, in ac-coupled operation for inactivity detection, a reference value is used for comparison and is updated whenever the device exceeds the inactivity threshold. After the reference value is selected, the device compares the magnitude of the difference between the reference value and the current acceleration with THRESH\_INACT. If the difference is less than the value in THRESH\_INACT for the time in TIME\_INACT, the device is considered inactive and the inactivity interrupt is triggered.

#### ACT\_x and INACT\_x Bits